Chip Learning:從芯片設(shè)計到芯片學習

|

|

中國網(wǎng)/中國發(fā)展門戶網(wǎng)訊 芯片是現(xiàn)代信息社會的關(guān)鍵基礎(chǔ)設(shè)施。絕大部分的電子設(shè)備——小到傳感器、大到超級計算機,以及我們每天用的手機、電腦,都是建立在芯片基礎(chǔ)之上的。從?20?世紀?60?年代開始,隨著半導體工藝的發(fā)展,芯片的復雜度快速增加,從只有少數(shù)晶體管的小規(guī)模開始快速發(fā)展到千百萬、數(shù)十億晶體管規(guī)模。例如,2020?年英偉達(Nvidia)發(fā)布的?A100?芯片集成了?500?多億晶體管。芯片制造工藝也已經(jīng)接近量子領(lǐng)域,臺積電(TSMC)的?5 nm?工藝已經(jīng)開始量產(chǎn)芯片,英特爾(Intel)等廠商已經(jīng)開展?2 nm?工藝的芯片研究。這些都離不開芯片設(shè)計的快速發(fā)展。

芯片設(shè)計本身是一個代價很高的過程。即使經(jīng)過了?40?多年的發(fā)展,也集成了越來越多的先進算法,芯片設(shè)計仍然是一個周期非常長、過程非常復雜、對設(shè)計人員專業(yè)度要求很高的任務(wù)。芯片制造本身的高額費用也加劇了對于芯片設(shè)計的要求。通常整個芯片設(shè)計流程,從立項到最后交付流片,中間涵蓋了邏輯設(shè)計、電路設(shè)計等復雜過程,大致需要?1—1.5?年的時間,需要包括系統(tǒng)設(shè)計人員、芯片設(shè)計人員、芯片開發(fā)人員、芯片驗證和測試工程師在內(nèi)的多名專業(yè)人員緊密地協(xié)作開發(fā)。

未來萬物互聯(lián)的智能時代需要大量不同種類的專用芯片。隨著智能時代的到來和“摩爾定律”的大幅度放緩,專用芯片的數(shù)量和種類大幅度增加,芯片體系結(jié)構(gòu)將要進入新的黃金時代,這對芯片設(shè)計提出了更大的挑戰(zhàn)。目前,深度學習處理器芯片就有很多種。例如:國外,谷歌(Google)推出了?TPU,英偉達推出?DLA?和包含專用加速?TensorCore?的多款?GPGPU,英特爾收購了?Neverana、Movidius?等多家公司,ARM、高通(Qualcomm)、蘋果(Apple)等公司的系統(tǒng)級芯片(SoC)也各自集成了自家的深度學習加速器硬件;國內(nèi),中科寒武紀科技公司推出了?Cambricon?云邊端系列芯片,阿里巴巴公司推出了含光?NPU,華為公司推出了達芬奇架構(gòu)芯片等。據(jù)統(tǒng)計,從?2014?年開始,全球深度學習處理器芯片就從一兩款增長到了幾百款之多。未來萬物互聯(lián)的智能時代對于大量種類和數(shù)量的芯片需求,也對芯片設(shè)計效率提出了新的挑戰(zhàn)。

如何解決芯片設(shè)計需求多和芯片設(shè)計代價高之間的矛盾?其中,最關(guān)鍵的問題是芯片設(shè)計領(lǐng)域?qū)υO(shè)計人員的專業(yè)水平要求比較高,既包括專業(yè)知識,也包括從業(yè)設(shè)計經(jīng)驗。如果芯片設(shè)計的“門檻”能降下來,那么任何一個稍加培訓的硬件設(shè)計人員就可以如同編寫軟件程序一樣快速地完成芯片設(shè)計。本文提出芯片學習(Chip Learning)來取代芯片設(shè)計可解決上述矛盾,即采用學習的方法來完成芯片從邏輯設(shè)計到物理設(shè)計的全流程。簡而言之,Chip Learning?針對這樣一類問題:輸入是簡單的功能需求描述(或者芯片的硬件程序),而輸出則是電路的物理版圖。Chip Learning?通過學習已有芯片設(shè)計進行訓練,根據(jù)輸入生成滿足要求的電路物理版圖。我們希望 Chip Learning 學習到的模型在使用時完全不需要專業(yè)知識和設(shè)計經(jīng)驗,可以在短時間、無人參與的情況下完成芯片設(shè)計。本文首先介紹現(xiàn)有芯片設(shè)計的流程,同時介紹近幾年人工智能(AI)技術(shù)在芯片設(shè)計中的應(yīng)用,在此基礎(chǔ)上說明實現(xiàn) Chip Learning 的思路和面臨的挑戰(zhàn)。

芯片設(shè)計流程和 Chip Learning

芯片設(shè)計流程

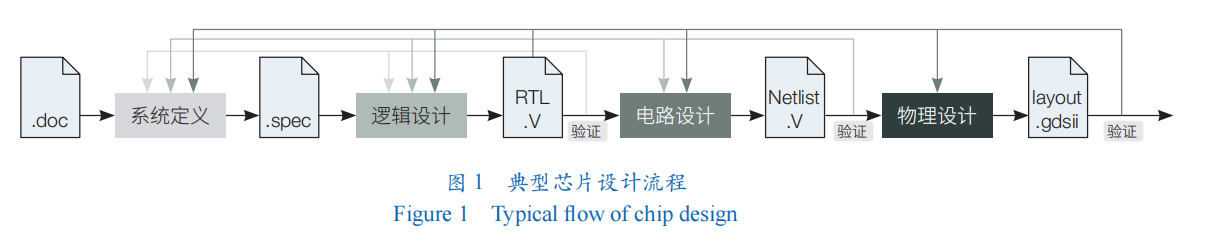

芯片設(shè)計是一個復雜的過程。通常,芯片設(shè)計指的是從需求出發(fā)最后生成版圖(layout)的過程。典型的芯片設(shè)計流程可以被簡單地劃分成?5?個階段(圖?1):①系統(tǒng)定義(chip specification)。給定需求后,進入系統(tǒng)定義階段,芯片設(shè)計人員確定設(shè)計參數(shù),并完成包括結(jié)構(gòu)、接口定義等具體設(shè)計。②邏輯設(shè)計(logic design)。由芯片開發(fā)人員根據(jù)系統(tǒng)定義進行邏輯設(shè)計,通常采用硬件開發(fā)語言?Verilog、VHDL?等實現(xiàn)芯片的硬件代碼,包括其中各個功能模塊、外部接口和整體連接。③電路設(shè)計(circuit design)。在得到芯片的硬件程序后,芯片開發(fā)人員進行電路設(shè)計,把硬件描述轉(zhuǎn)換成為門級的電路表示。④物理設(shè)計(physical design)。在得到芯片網(wǎng)表之后,芯片開發(fā)人員進行物理設(shè)計,把門級網(wǎng)表轉(zhuǎn)換成物理實現(xiàn)表示,即芯片的版圖;其常見格式為圖數(shù)據(jù)表示,即?graphic data systemⅡ(GDSⅡ)。另外,芯片開發(fā)人員會在物理設(shè)計的各個階段進行驗證測試和迭代設(shè)計,以得到符合需求的芯片設(shè)計。⑤驗證測試(test & verification)。最終完成的芯片版圖送至代工廠進行制造,后續(xù)再進封裝、制板、測試等工序,這樣就得到了一顆完整的芯片。

2. Chip Learning

近些年來,以深度學習為代表的?AI?技術(shù)再次興盛,已經(jīng)在很多任務(wù)上表現(xiàn)出卓越的效果。例如,ResNet-512?深度學習模型在圖像識別上表現(xiàn)出超越人的識別能力,DeepMind?公司提出的?AlphaGo?系列模型在圍棋游戲上表現(xiàn)超越人類棋力。研究人員也開始研究將最新的?AI?技術(shù)應(yīng)用到芯片設(shè)計當中,如深度神經(jīng)網(wǎng)絡(luò)、強化學習、生成對抗網(wǎng)絡(luò)等。這一方向也受到越來越多的關(guān)注。Cadence?公司已經(jīng)在?2020?年發(fā)布了iSpatial 引擎,以支持機器學習進行統(tǒng)一布局布線和優(yōu)化。Synopsys?公司也在?2019?年推出了?DSO.ai?工具,其基于?AI?技術(shù)極大地提升了芯片設(shè)計效率。

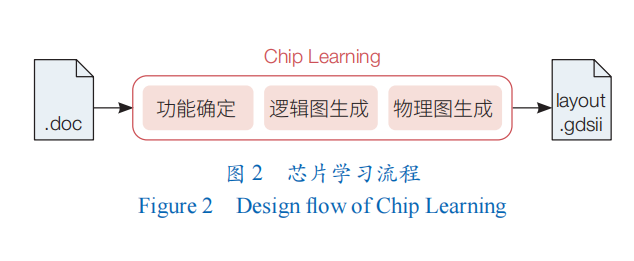

然而,目前全球芯片設(shè)計中的深度學習工作還主要停留在采用人工智能技術(shù)去輔助解決傳統(tǒng)芯片設(shè)計流程中的子問題,如評估、預測芯片設(shè)計的結(jié)果等。與之不同的是,本文提出的?Chip Learning?技術(shù)內(nèi)涵則是取代傳統(tǒng)芯片設(shè)計流程,通過?AI?模型學習專業(yè)知識,從而實現(xiàn)無人化(no-man-in-the-loop)芯片設(shè)計(圖?2)。具體而言,類比傳統(tǒng)芯片設(shè)計流程,Chip Learning?可以分成?3?個重要問題:①功能生成。當用戶用模糊的語言確定了系統(tǒng)功能,第一個重要的問題就是根據(jù)用戶意圖確定系統(tǒng)正確的功能,并生成系統(tǒng)的準確表達。這種準確表達可以是硬件代碼,也可以是表達式,也可以是真值表。這個問題對應(yīng)著傳統(tǒng)芯片設(shè)計流程的邏輯設(shè)計。②邏輯圖生成。當有了準確表達,第?2?個重要的問題就是要生成電路的邏輯圖表達,并在這張邏輯圖上進行優(yōu)化,最后生成物理無關(guān)(包括工藝)的邏輯圖表達。這個問題對應(yīng)著傳統(tǒng)芯片設(shè)計流程的電路設(shè)計。③物理圖生成。當有了電路邏輯圖后,第?3?個重要的問題就是要生成電路的具體物理版圖,這等價于一種多種約束下(如面積、功耗、物理等限制)的圖映射和優(yōu)化問題。這個問題對應(yīng)著傳統(tǒng)芯片設(shè)計流程的物理設(shè)計。

芯片學習在芯片設(shè)計流程中需要解決的問題

邏輯設(shè)計

邏輯設(shè)計的核心就是要得到電路的硬件描述。通常這一過程通過人工完成,也就是硬件開發(fā)人員采用硬件描述語言如?Verilog、VHDL?手動編寫?RTL?的硬件程序。還有一種方法就是高層次綜合(HLS)。高層次綜合指的是通過高層次綜合工具把?C、C++或者?SystemC?等高級編程語言描述的硬件功能轉(zhuǎn)化成為硬件描述語言?Verilog、VHDL?程序。傳統(tǒng)高層次綜合算法一般通過確定性的方法對高級語言進行變換。近些年來,除了傳統(tǒng)的機器學習算法如支持向量機(SVM),最新的人工智能技術(shù)如深度神經(jīng)網(wǎng)絡(luò)(DNN)、圖神經(jīng)網(wǎng)絡(luò)(GNN)也被用于高層次綜合中,主要用于幫助更快速的?HLS?設(shè)計結(jié)果評估(質(zhì)量估計、性能估計、時序估計、資源開銷估計)和?FPGA?設(shè)計空間搜索優(yōu)化。

與上述?2?種方法相比,芯片學習更進一步:當用戶給定模糊描述后,通過猜測用戶意圖自動編寫硬件程序,或者說自動生成硬件的準確表達——可以是硬件?RTL?程序,也可以是硬件表達式,還可以是硬件真值表。這其中面臨很多挑戰(zhàn),如用戶意圖的確定,硬件表達的準確性等。在該方面,程序綜合(program synthesis)——自動構(gòu)建由指定語言構(gòu)成的、符合用戶某種要求的程序,跟芯片學習的功能確定問題具有同樣的形式。目前,程序綜合已經(jīng)有了很多進展可供芯片學習借鑒參考。

電路設(shè)計

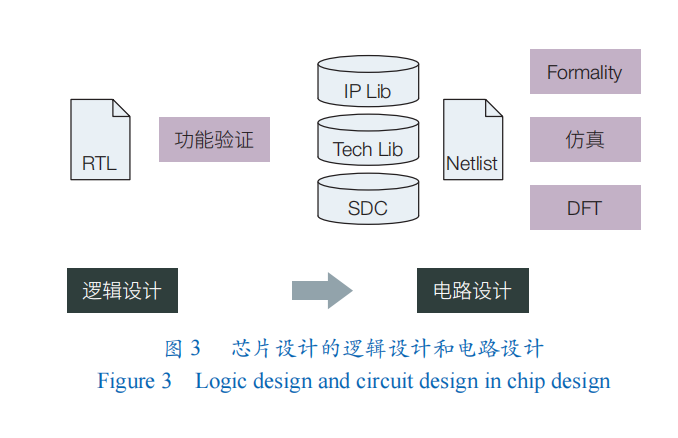

在得到芯片的硬件描述后,芯片開發(fā)人員進行電路設(shè)計。如圖?3?所示,在電路設(shè)計中,電路的硬件描述程序會被轉(zhuǎn)化成為電路圖(網(wǎng)表),這個過程也被稱為前端設(shè)計(front-end processing)或者綜合(synthesis)。

電路設(shè)計包含?2?個核心優(yōu)化步驟:邏輯最小化和物理映射。邏輯最小化指對電路的布爾表達式和邏輯網(wǎng)表結(jié)構(gòu)進行化簡,從而得到盡可能小的邏輯表達式。物理映射則是在給定物理工藝庫的情況(如可用的門的種類、標準單元),把邏輯表達式映射到這些物理單元上,生成盡可能簡單的物理電路。當前,芯片設(shè)計中利用?AI?技術(shù)可實現(xiàn)的相關(guān)工作主要集中在這?2?個核心優(yōu)化步驟上。LSOracle?采用深度神經(jīng)網(wǎng)絡(luò)(DNN)去動態(tài)決定電路中不同部分是采用?And-Inverter Graph?還是?Majority-Inverter Graph?優(yōu)化器。Haaswijk等和Zhu等把邏輯優(yōu)化問題定義成馬爾可夫決策過程(Markov decision process),采用深度強化學習框架,圖卷積神經(jīng)網(wǎng)絡(luò)作為策略,來實現(xiàn)邏輯優(yōu)化。Hosny?等則采用強化學習里的演員-評論家模型(A2C)來尋找時序約束下最小化面積開銷的邏輯最小化方案。Deep-PowerX?通過?DNN?來預測部分電路采用近似電路時的電路輸出錯誤率,從而盡可能地降低電路的動態(tài)功耗。

芯片學習在這個階段要解決的問題是邏輯圖生成,也即在給定電路的硬件描述(如?RTL?程序、表達式或真值表)和可用節(jié)點類型的約束下,生成電路相應(yīng)的邏輯圖。在該邏輯圖中,節(jié)點是門、宏單元、已知功能模塊,連線是有方向的,表示信號從一端流向另外一端。如果是時序電路,邏輯圖中還會存在環(huán)路。同樣的,在該邏輯圖上需要做優(yōu)化,以盡可能地去掉電路中的冗余,保證生成的邏輯圖盡量精簡。一個思路是采用傳統(tǒng)編譯的思路完成這個過程,并采用上文類似的?GNN?和增強學習(RL)方法實現(xiàn)圖級別優(yōu)化。另外一個思路是采用神經(jīng)編譯器(neural compiler),直接替代傳統(tǒng)的編譯技巧,把輸入轉(zhuǎn)化成為邏輯圖并在圖上做進一步的優(yōu)化,從而得到更簡潔的邏輯圖表達。

物理設(shè)計

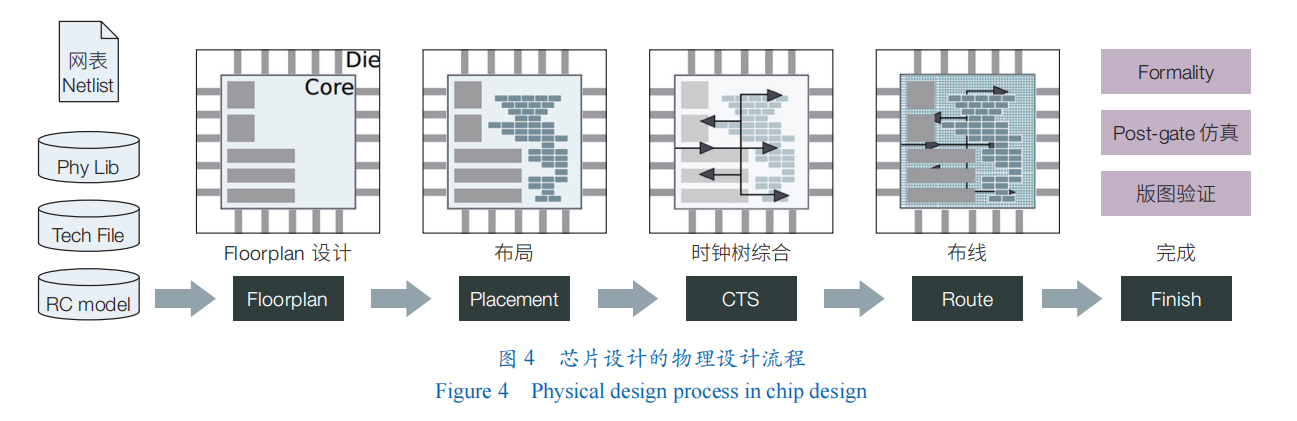

在得到芯片網(wǎng)表之后,芯片開發(fā)人員開始進行物理設(shè)計;其把門級網(wǎng)表轉(zhuǎn)換成物理元器件及其連線并固定下來,最后得到芯片的版圖。物理設(shè)計流程比較復雜(圖?4),不同工藝還有其獨特的地方,主要包括?floorplan?設(shè)計、布局(placement)、時鐘樹綜合(CTS)、布線(route)、完成(finish)。在開始物理設(shè)計之前,設(shè)計人員需要先確定物理設(shè)計環(huán)境,包括設(shè)計所需要的物理庫(physical library)、工藝(technology file)、設(shè)計約束庫(constraints file)等;芯片設(shè)計相關(guān)的參數(shù),包括設(shè)計采用的工藝、芯片采用幾層金屬、最小線間距、所允許的最大扇出(fanout)等。

物理設(shè)計本身流程多、復雜,子問題也多,因此采用AI技術(shù)解決其中子問題的研究工作也相對多一些。在布局中,AI?技術(shù)主要被用來生成更好的布局和預測布局后的結(jié)果。例如,在?2021?年發(fā)表的電路后端設(shè)計自動化的工作中,谷歌把布局問題形式化為序列決策問題,從而利用強化學習的方法來解決,不到?6小時即可生成具有媲美或超過人工的現(xiàn)代加速器網(wǎng)表上的布局。He?和?Bao使用強化學習訓練一個?Agent?幫助選擇空間搜索時下一步訪問的鄰居節(jié)點,用以指導生成更好的布局。在時鐘樹綜合中,AI?技術(shù)的應(yīng)用主要關(guān)注對生成的時鐘樹做優(yōu)化或預測。Lu?等提出采用生成對抗網(wǎng)絡(luò)(GAN)和強化學習來預測、優(yōu)化生成的時鐘樹,從而降低時鐘漂移和時鐘樹長度。Nagaria?和?Deb、Kwon等分別采用卷積神經(jīng)網(wǎng)絡(luò)(CNN)、DNN?來預測時鐘樹組件,如?gatingg?單元、buffer?數(shù)量、wireloads?等,從而幫助提高時鐘樹質(zhì)量,降低時鐘樹長度、時鐘漂移等。在布線中,人工智能技術(shù)主要被用來布線結(jié)果預測和評估。Liang等和Alawieh等將問題化為?image-to-image?問題,分別用?CNN?和條件生成對抗網(wǎng)絡(luò)(CGAN)進行布線堵塞預測。在完成階段,AI?技術(shù)主要用于驗證測試中的時序分析、信號完整性分析和功耗分析方面。Barboza等用隨機森林方法使時序分析可以脫離手工特征進行,同時減小布線前時序估計的誤差。Ambasana等、Lu等、Goay?和?Goh的多篇工作都以眼圖的寬高用神經(jīng)網(wǎng)絡(luò)為基礎(chǔ)預測電路信號串擾或抖動。

芯片學習對應(yīng)的子問題是物理圖生成。可以看到,在物理設(shè)計的多個階段,AI技術(shù)被廣泛地用來輔助解決其中的子問題,芯片學習則期望能夠直接端到端得到一個最終的物理版圖。這個子問題的難度可想而知,其中涵蓋了多個子問題,也極有可能需要多個模型協(xié)同進行工作,才有可能最終解決。利用芯片學習端到端得到最終物理版圖的挑戰(zhàn)主要有?2?個方面:①問題和約束形式化較為困難。正如上面芯片物理設(shè)計流程中所介紹的一樣,問題本身的輸入是類似網(wǎng)表的邏輯圖,最終輸出的是物理版圖。不同規(guī)模的電路蘊含的功能也不一樣,這就意味著統(tǒng)一的模型能夠處理變長、變規(guī)模的輸入和輸出。另外,物理設(shè)計中的約束也是多種多樣的,包括:芯片本身的最大面積、所能容忍的最大延遲等基本約束,以及電源網(wǎng)絡(luò)構(gòu)建、crosstalk?消除、天線效應(yīng)等約束。這些約束需要變成結(jié)構(gòu)化的信息從而可以被人工智能模型所接受,也即計合理的數(shù)據(jù)結(jié)構(gòu),這也是非常困難的。②問題對應(yīng)的解空間規(guī)模大。電路物理設(shè)計過程中本身就包含了很多復雜度很高甚至于是?NP?完全問題,這也就意味著物理設(shè)計本身是一個隨著規(guī)模增大復雜度急劇上升的問題。

對于解決芯片學習物理版圖生成這個非常困難的問題,目前已經(jīng)看到了一些曙光。谷歌使用?RL?和GNN?替代了傳統(tǒng)的布局過程,Liao等、He和Bao也提出了直接替代布線過程的小規(guī)模電路上的方案,從而證明了?AI?技術(shù)在傳統(tǒng)問題上大有可為。物理版圖最終是要針對工藝的,而值得慶幸的是,現(xiàn)在芯片設(shè)計流程中的設(shè)計規(guī)則是抽象出來與工藝無關(guān)的約束規(guī)則,這也將是芯片學習解決方案未來能夠泛化到不同工藝上的基礎(chǔ)。

驗證測試

驗證測試貫穿整個芯片設(shè)計流程。在不同階段,芯片開發(fā)人員都需要對得到的設(shè)計進行反復驗證,如功能測試驗證、邏輯測試驗證、電路測試驗證、網(wǎng)表測試驗證、版圖測試驗證。

對于芯片學習而言,驗證測試核心要解決的挑戰(zhàn)就是黑盒解決方案的精度保證。現(xiàn)有的?AI?技術(shù)雖然能在很多問題上達到很好的效果,但其為人所詬病的一點就在于這些黑盒模型缺乏可解釋性,對于輸出結(jié)果的精度也無法給出理論的保證。這一點對于芯片學習尤其重要,因為芯片流片的成本非常高,即使未來在工程上芯片學習能夠解決問題,AI?新技術(shù)的可解釋性也需要繼續(xù)深入研究。

未來工作

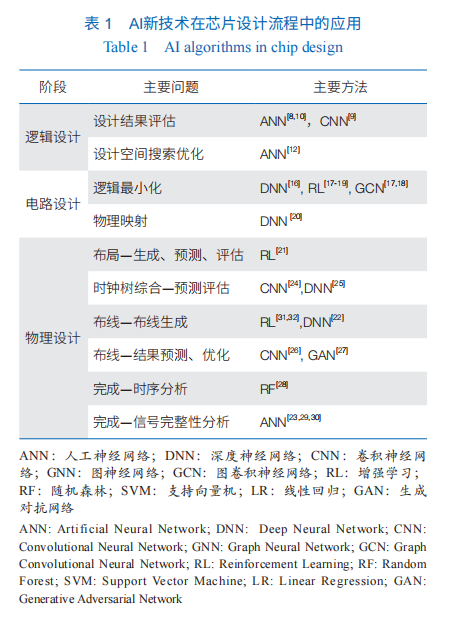

芯片學習是萬物互聯(lián)的智能時代解決芯片設(shè)計需求大和代價高之間矛盾的核心方法。目前,AI?新技術(shù)在芯片設(shè)計流程中已經(jīng)得到應(yīng)用(表1),然而這些工作都還是集中在芯片設(shè)計各個環(huán)節(jié)當中的子問題,主要是輔助傳統(tǒng)設(shè)計流程,完成預測、評估方面的功能,尚未實現(xiàn)?AI?取代傳統(tǒng)芯片設(shè)計流程;芯片學習則是希望能夠完全取代傳統(tǒng)芯片設(shè)計流程,用?AI?模型學習專家知識,大幅度降低芯片設(shè)計門檻,提升芯片設(shè)計效率,從而實現(xiàn)端到端的快速無人化芯片設(shè)計。

芯片學習未來有?3?點主要工作。全流程。芯片學習在各個流程上實現(xiàn)取代傳統(tǒng)算法,同時在各個流程中消除人的參與,從而實現(xiàn)芯片設(shè)計全流程無人化以節(jié)省人力資源,實現(xiàn)高效率的芯片設(shè)計。跨層次優(yōu)化。利用芯片學習,希望將芯片設(shè)計各個環(huán)節(jié)打通實現(xiàn)跨層次設(shè)計與優(yōu)化,實現(xiàn)大規(guī)模芯片統(tǒng)一設(shè)計,從而實現(xiàn)更優(yōu)的芯片設(shè)計。并行加速。AI?技術(shù)以計算量大、數(shù)據(jù)量大著稱,而芯片設(shè)計又是非常復雜的任務(wù),芯片學習也需要研究并行和加速方法。例如,采用已經(jīng)蓬勃發(fā)展的人工智能芯片,從而保證芯片設(shè)計效率。未來,芯片學習希望實現(xiàn)從設(shè)計芯片到自動生成芯片的轉(zhuǎn)變,更好地支撐智能萬物互聯(lián)時代的應(yīng)用需求。

(作者:陳云霽,中國科學院計算技術(shù)研究所 計算機體系結(jié)構(gòu)國家重點實驗室、中國科學院大學 計算機科學與技術(shù)學院;杜子東、郭崎、李威,中國科學院計算技術(shù)研究所 計算機體系結(jié)構(gòu)國家重點實驗室;譚懿峻,中國科學院計算技術(shù)研究所 計算機體系結(jié)構(gòu)國家重點實驗室、中國科學院大學 計算機科學與技術(shù)學院;《中國科學院院刊》供稿)